Giáo sư Kenichi Okada và các cộng sự tại Viện Công nghệ Tokyo đã hợp tác với Viện Công nghệ Thông tin và Truyền thông Quốc gia để nghiên cứu và phát triển chip thu phát sóng không dây sử dụng băng tần D mới theo quy trình 65 nm và công nghệ CMOS (bán dẫn oxit kim loại bổ sung silicon). Kết quả nghiên cứu được trình bày tại Hội thảo IEEE 2024, diễn ra ngày 16-20/6 tại Honolulu, Mỹ.

Theo Okada, điểm đáng chú ý của chipset là việc đạt được tốc độ cao chỉ bằng công nghệ CMOS giá rẻ, giúp tiết kiệm chi phí khi sản xuất hàng loạt.

Công nghệ kết nối 5G hiện cho tốc độ cao nhất 10 Gbps và hoạt động ở các băng tần 24-47 GHz, còn các công nghệ kết nối thế hệ tiếp theo đang phải nghiên cứu và phát triển trên các băng tần cao hơn. Trong khi đó, chipset mới của Nhật Bản được phát triển để hoạt động trên băng tần từ 114 đến 170 GHz với băng thông tín hiệu 56 GHz.

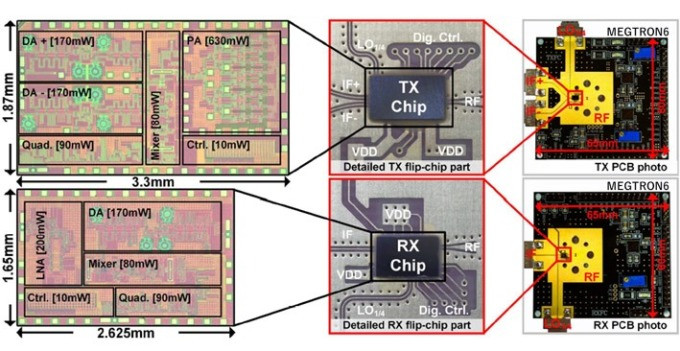

Các nhà nghiên cứu sử dụng bảng mạch tích hợp để tạo một thiết bị thu và một thiết bị phát với IC dành cho bộ phát có kích thước 1,87 x 3,3 mm và IC cho bộ thu là 1,65 x 2,6 mm. Ngoài ra, bảng mạch có bộ khuếch đại công suất để nâng tín hiệu lên mức phù hợp, bộ khuếch đại nhiễu thấp để tăng cường tín hiệu, bộ biến tần để điều chỉnh tín hiệu theo dải tần...

Trong thử nghiệm với cấu hình nhiều đầu vào và đầu ra (MIMO), các nhà nghiên cứu sử dụng bốn modul máy phát và bốn modul máy thu, trong đó mỗi ăng-ten có thể xử lý luồng dữ liệu riêng. Khi sử dụng điều chế 16QAM, tốc độ mỗi kênh đạt 160 Gbps và tổng tốc độ đạt được 640 Gbps, nhanh hơn 100 lần so với hệ thống 5G hiện có trên thị trường.

Công trình nghiên cứu này được hỗ trợ một phần bởi Bộ Nội vụ và Truyền thông Nhật Bản. Kenichi Okada cho biết: "Chipset hứa hẹn là hệ thống không dây thế hệ tiếp theo hỗ trợ ôtô tự động, y tế từ xa và trải nghiệm thực tế ảo tiên tiến".

Ý kiến ()